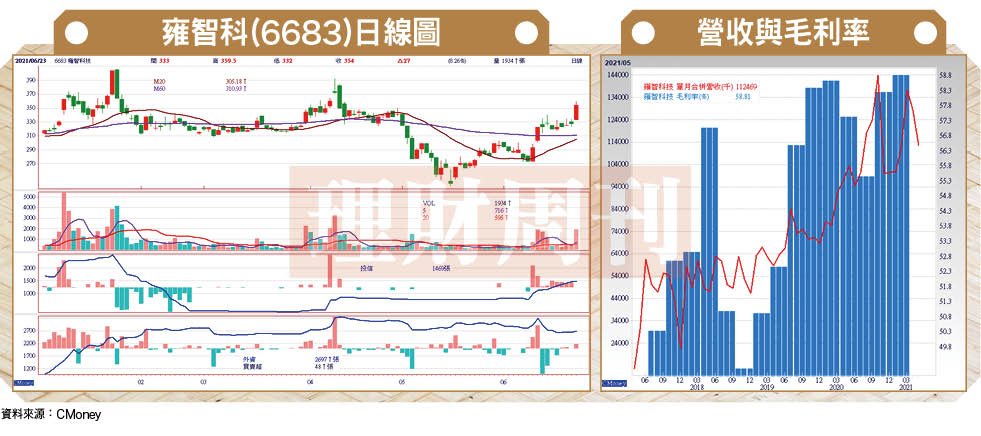

蘋果新增MacBook/iPad Pro「Apple Silicon」處理器代工需求,帶動台積電先進封裝製程更為搶手,而台積電擴產滿足客戶代工需求,相關先進製程供應鏈後市營運成長可期。

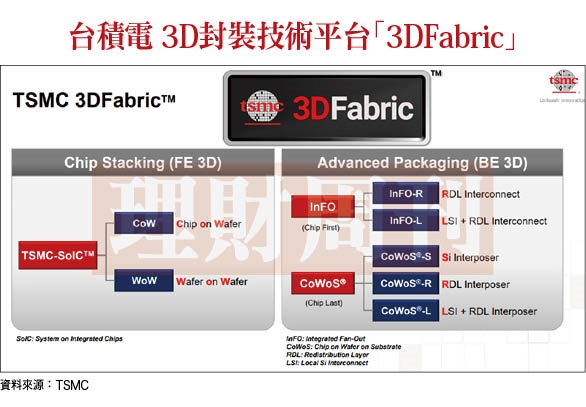

全球半導體晶圓代工業龍頭廠台積電(2330),去年已將先進封裝技術,進一步整合至「3DFabric」服務平台,包括:台積電前段3D矽堆疊技術「TSMC-SoIC」,以及包含「基板上晶圓上晶片封裝(CoWoS)」與「整合型扇出(InFO)後段導線連結技術」所組成,提供給客戶的「整合異質小晶片(chiplet)」彈性解決方案。

台積電「TSMC-SoIC」同時提供WoW、CoW先進封裝製程,可同時堆疊同質、異質晶片,大幅提升系統運作效能,並進一步縮小產品IC晶片尺寸。台積電WoW技術,已成功在去年於邏輯對記憶體及邏輯對深溝槽電容(DTC)的「垂直異質整合」上,展現出優異電性表現。七奈米晶圓WoW製程,預期可於今年第四季完成認證。

台積電目前正持續加速3DIC先進封裝技術製程推進速度。屬於前段3D領域、台積電系統整合晶片封裝(TSMC-SoIC)項目的「晶圓堆疊晶圓(WoW)」、「晶片堆疊晶圓(CoW)」等先進封裝技術,將於今年第四季,完成七奈米製程晶圓、晶片的「堆疊封裝技術」認證。產業界人士分析,台積電將可坐穩高效能運算(HPC)處理器的先進製程晶圓代工、晶圓級封裝市場龍頭寶座,同時明顯拉開與市場其他競爭對手的技術距離。

針對5G智慧型手機等行動應用領域,台積電推出「InFO_B(bottom only)」解決方案,將效能強大的行動處理器,進一步整合於輕薄精巧的IC封裝之中,以提供強化的效能與運轉功耗效率,並且支援行動裝置製造廠商,於IC封裝時所需的DRAM堆疊製程配置。

台積電已於去年正式量產第五代「整合型扇出層疊封裝(InFO-PoP Gen5)」,以支援行動裝置應用需求,同時已獲得蘋果(Apple)A14AP處理器採用。台積電亦已量產第二代「整合型扇出暨基板封裝技術(InFO-oS Gen2)」,以支援HPC運算晶粒的分割應用。第六代InFO-PoP已成功通過認證,支援行動應用、增強散熱性能所需。同時,如期開發完成的第三代InFO-oS,亦提供更多的晶片分割服務,可整合於更大的封裝尺寸、滿足更高的頻寬需求。

台積電CoW製程研發仍持續進行中,七奈米對七奈米的CoW堆疊製程,可望於今年第四季完成認證,並且準備就緒。五奈米對五奈米CoW堆疊製程,則預計於二○二二年第三季準備就緒。台積電現階段正加快苗栗竹南封裝廠AP6的建廠作業,該廠總面積,為台積電其它四座封測廠總面積一.三倍,二○二二年下半年,可開始量產包含CoW在內,「TSMC-SoIC」先進封裝製程IC晶片。

由於新冠肺炎疫情的影響,全球數位轉型速度因而加快,加以5G智慧型手機、物聯網裝置日益普及之下,雲端運算、伺服器配置需求正持續轉強,高效能運算(HPC)處理器的出貨,進入高速成長期。

全球晶圓代工龍頭台積電,於看好HPC應用後市具強勁成長動能下,因而於前段晶圓製造領域,積極擴建七奈米、五奈米晶圓代工產能,配合後段先進封裝「3DFabric」平台布局的同步開展,代工服務業務接單已一路暢旺至今年底。

台積電於年報中已指出,於巨量數據運算、應用創新的市場力量驅動下,HPC高速運算已成為台積電業務增長的主要動力之一。

台積電持續為IC設計廠、系統廠等客戶,提供全球領先的晶圓代工製造技術,如:五奈米、七/六奈米、一六/一二奈米鰭式場效電晶體(FinFET)等邏輯IC代工製程技術,以及包含高速互連技術等完備、充足的矽智財(IP),以滿足客戶產品應用於任何地點、時間,傳輸及處理大量資料的運算需求。

伴隨台積電七奈米、五奈米等先進晶圓代工製程產能的大量開出,多種HPC運算處理器已因此獲得導入市場,包括:中央處理器(CPU)、繪圖處理器(GPU)、伺服器處理器、可程式邏輯閘陣列(FPGA)、人工智慧(AI)加速器、高速網路晶片等,下游巾場應用範圍涵括:雲端運算、資料中心、5G、AI終端及局端裝置等領域,包含:英特爾(Intel)、超微(AMD)、輝達(AMD)、博通(Broadcom)、賽靈思(Xilinx)、聯發科(MediaTek)等都是台積電主要客戶。

為有效提升HPC高速運算效能,台積電提供涵括:「基板上晶圓上晶片封裝(CoWoS)」、「整合型扇出封裝(InFO)」,以及「台積電系統整合晶片(TSMC-SoIC)」等多種「3DFabric」平台的先進IC整合封裝技術,協助客戶完成異質、同質晶片整合封裝,以幫助客戶以最快速度,充分、及時掌握HPC運算領域市場成長商機。

有關先進封裝技術發展部分,台積電持續擴展由三維(3DIC)矽堆疊、先進封裝技術所組成,完備的3DFabric系統整合解決方案。針對HPC高速運算應用,台積電今年將提供更大光罩尺寸服務,以支援整合型扇出暨封裝基板(InFO_oS)、CoWoS封裝解決方案,運用更大範圍的布局規畫,以有效整合小晶片(chiplet)、高頻寬記憶體(HBM)封裝構體。

台積電將於今年下半年,針對二.五個光罩尺寸的InFO製程進行驗證,以涵括HPC運算要求、更廣泛的布局規畫。台積電預計於今年提供三個光罩尺寸,用以強化CoWoS封裝技術,開發更具成本效益的CoWoS-R、CoWoS-L製程,以滿足HPC應用、各種小晶片與HBM記憶體的整合封裝需求。

5G應用成長、HPC市占率拉高 成台積電未來持續成長主力

本土法人先前已預估,隨著蘋果(Apple)新世代處理器Apple Silicon,採用台積電所提供「InFO_oS(整合型扇出暨載板封裝)」CPU處理器晶圓代工及封裝解決方案,預料也將因此帶動全球高階製程IC晶片,採用「3D IC封裝」先進製程應用風潮,如此一來,預料相關供應鏈台廠後市也將受惠可期。

另一方面,主要應用於行動通訊裝置處理器晶圓代工的「InFO_PoP(整合型扇出層疊封裝)」技術,則不需要使用載板,且外形輪廓更為輕薄,電力、散熱效果亦更好。

相較之下,InFO_oS封裝技術仍需使用載板封裝,以增強IC晶片間的連接效能。InFO_oS為「多晶片端對端整合」解決方案,晶圓代工廠利用InFO技術,可以將HPC(高速運算)、網路應用的數個先進邏輯小晶片(chiplet),進一步整合至65mm * 65mm載板完成封裝。

隨著Apple Silicon的即將問市,由於僅有單一晶圓代工廠可大規模接單的情勢已底定,國內法人機構因此將台積電,視為本波高階晶圓代工商機的最大受惠廠。蘋果先前於全球開發者大會中提及,Mac系列產品將從Intel X86架構,完全轉換至ARM架構的Apple Silicon晶片,轉換時間約需三年期間,因此,本土法人預測今年新款Apple Silicon晶片的第一年搭售率,約為三○%~五○%。供應鏈業者調查顯示,新款iPad Pro也將搭載A14X ARM架構CPU晶片。

3D IC封裝先進製程產能增加 相關台廠供應鏈受惠可期

在過去幾年之中,蘋果(Apple)相關晶圓代工訂單,對台積電整體營收的貢獻度,約持穩於二二%~二三%左右;然而,伴隨新進晶圓代工業務持續發展下,預估蘋果對台積電的貢獻度,將進一步成長達二四%~二九%左右。

由於預期蘋果於收購Intel旗下原有基頻業務單位後,將會推出更多自有(自主研發)晶片組,如:自行設計智慧型手機用基頻數據機晶片,國內法人機構因而認為,後續對台積電的營運貢獻度將不僅只於此。整體而言,預估5G應用持續成長、HPC市占率不斷拉高下,將成為台積電未來幾年營運持續成長的助攻主力部隊。

伴隨蘋果新增MacBook/iPad Pro「Apple Silicon」處理器代工需求,台積電原本供應iPhone 12用「A14」AP處裡器,恐將供不應求、「3D IC封裝」先進製程之一的「整合型晶圓級扇出封裝(InFO)」封裝製程,勢必因此同步於「3DFabric」平台,擴增產能規模,以滿足客戶新增代工需求。如此一來,台積電進一步增加支出、擴增高階先進晶圓代工、封裝製程產能後,相關「台積電先進製程相關供應鏈」族群股,後市營運將可望因此再獲挹注新一波成長動能。